1. Jurnal [Kembali]

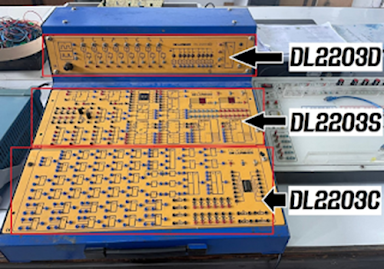

2. Alat dan Bahan [Kembali]

3. Rangkaian [Kembali]

4. Prinsip Kerja Rangkaian

[Kembali]

Counter Asyncronous disebut juga Ripple Through Counter atau Counter

Serial (Serial Counter), karena output masing-masing flip-flop yang digunakan

akan bergulingan (berubah kondisi dari “0” ke “1”) dan sebaliknya secara

berurutan atau langkah demi langkah, hal ini disebabkan karena hanya flipflop

yang paling ujung saja yang dikendalikan oleh sinyal clock, sedangkan

sinyal clock untuk flip-flop lainnya diambilkan dan masing-masing flip-flop

sebelumnya

5. Video Rangkaian [Kembali]

6. Analisa [Kembali]

1. Analisa output percobaan berdasarkan IC yang digunakan ?

Jawab :

Pada percobaan ini menggunakan IC 74LS112 yang mana merupakan rangkaian JK flip flop yang memiliki prinsip kerja output akan berubah ketika clock dihubungkan. Jadi pada percobaan 1 ini ketika kondisi toggle, didapatkan outputnya naik atau bisa disebut counter UP ,dimana perhitungannya dimulai dari 0 - 15.

2. Analisa sinyal output yang dikeluarkan JK flip flop kedua dan ketiga!

Jawab :

Jadi pada rangkaian Counter Asyncronous yang disusun dengan JK flip flop ini, output yang dihasilkan itu akan berurutan , dimana cara kerjanya JK flip flop kedua menunggu inputan dari output pertamaa dan JK flip flop ketiga menunggu inputan dari output JK flip flop yang kedua.

7. Link Download [Kembali]

link Video [ klik ]

link datasheeet 74LS112 [ klik ]

link datasheet switch [ klik ]

link datasheet LED [ klik ]

.png)

Tidak ada komentar:

Posting Komentar